- 電気電子回路が分からないので、実際に回路を試しながら理解するのに何か便利なものはないかと探していたら、電子回路のアナログ動作をシミュレーションするソフトウェアがある事を知り、先ず OrCAD を見つけました。

OrCAD Capture CIS (32bit版)をダウンロード。

手持ちのトランジスター 2SC1815 が OrCAD のライブラリーには無かったのでライブラリーの登録の参考ページで試すが理解力が無いために旨く登録できず、OrCAD を諦めました。

- 次に試したのは、LTspice XVII でした。Windows 7,8 and 10 用をダウンロード。

OrCAD のLite無料版は制限があり、2016年以降新版が出ていないようですが、LTspice XVII は一切の制限がなく直近のものは、2019年9月19日でした。

ライブラリーの登録は分かりやすく問題なく行き LTspice に反映された。

インターネット上の情報量は、LTspice の方が圧倒的に多い様子です。

以上の結果から LTspice で試すことにしました。

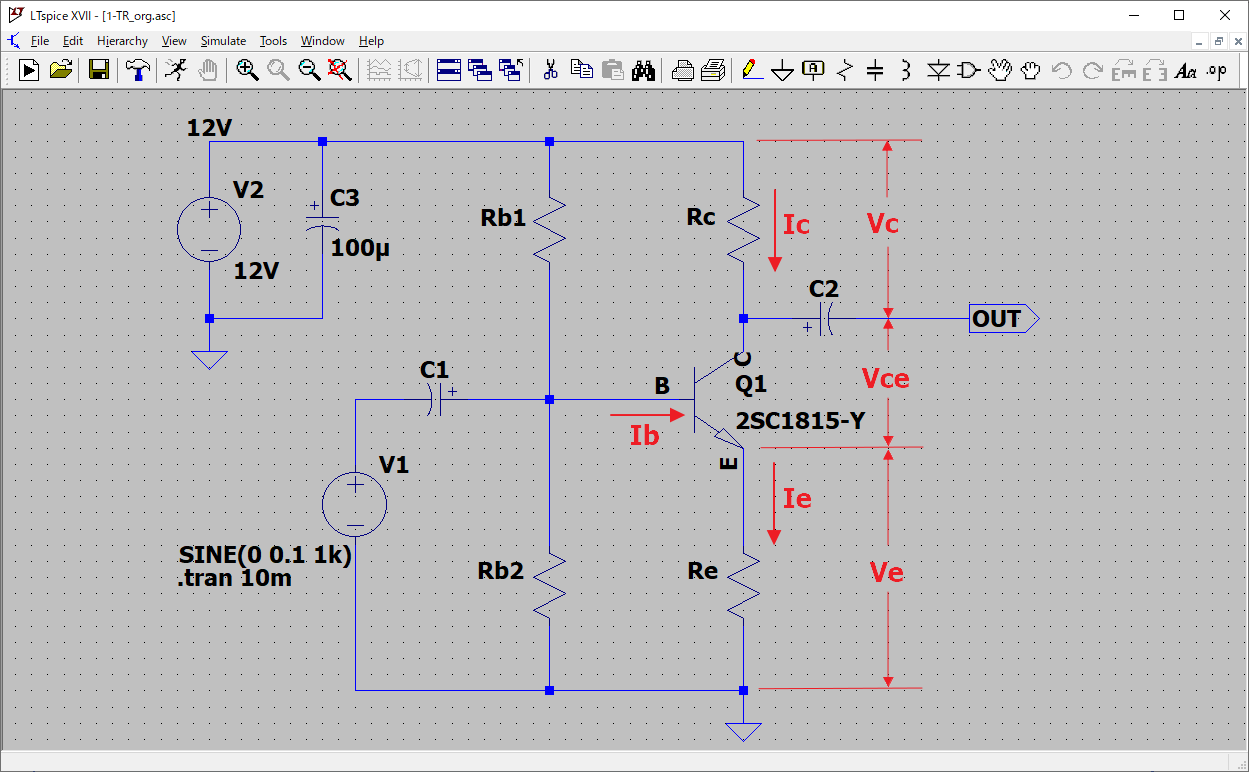

- 増幅回路はエミッタ共通回路、バイアスは電流帰還バイアスで試してみます。

|

|

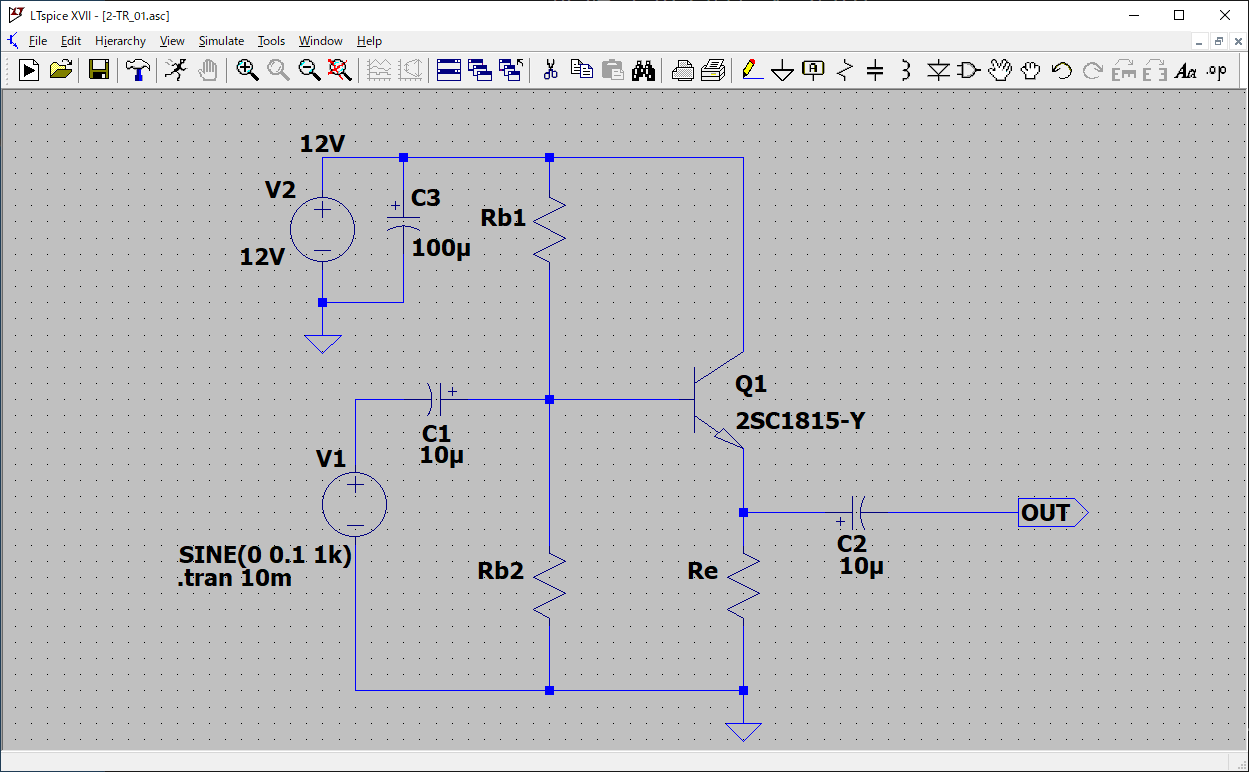

- 初段 トランジスタ回路

- シミュレーション設定内容

電源(VCC) :12V

信号源は :100mV 1kHz サイン波

トランジェント解析: Stop Time 10msec

- 2SC1815

低周波電圧増幅用 励振段増幅用

VCEO=50V(最小)、IC=150mA(最大)

hFE(2)=100(標準) (VCE=6V、IC=150mA)

- まず以下の回路図を作成

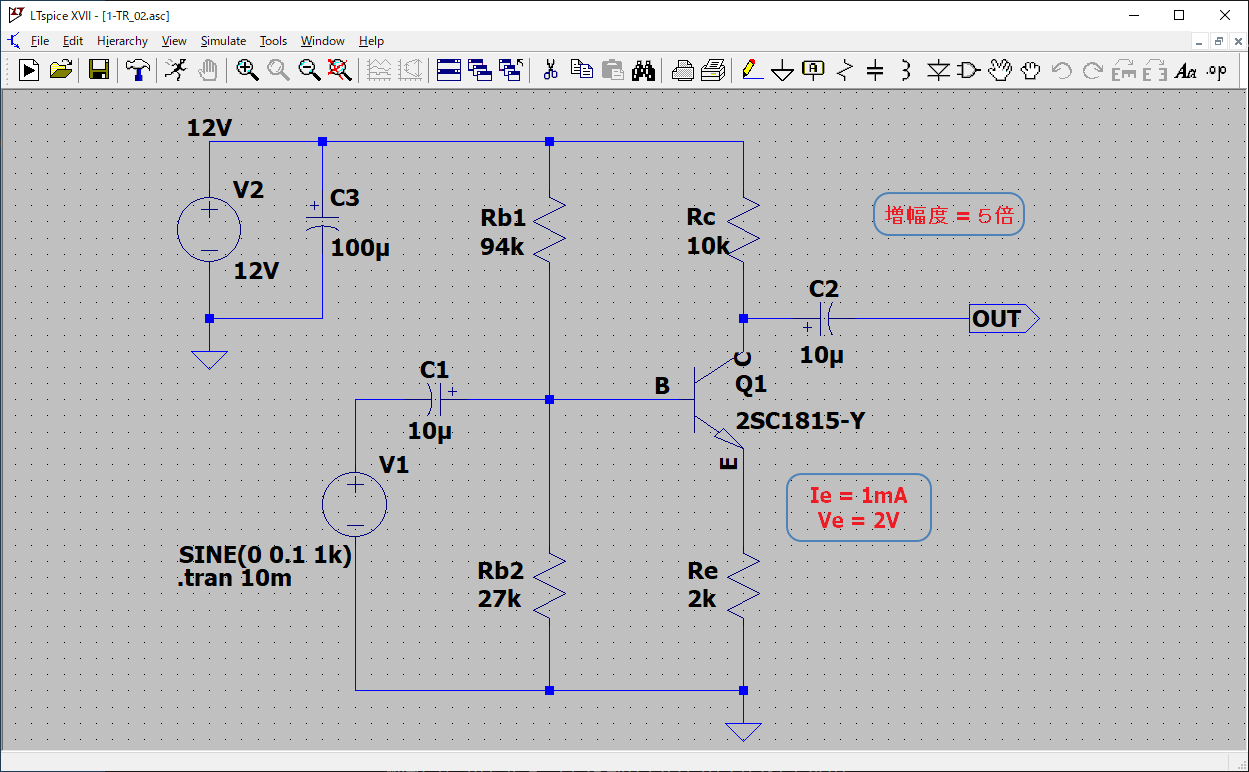

- 最初にエミッター電流 Ie を 1mA 、Reの電圧降下を2Vに設定してみます。つまり Ve=2V です。

- Re=Ve÷Ie=2KΩ、Rc は Ie≒Ic として Rc=(12V-2V)÷1mA≒10KΩ よって電圧増幅度(交流利得)は Rc÷Re=10KΩ÷2KΩ=5、増幅度は 5倍になる予定です。(Vbe≒0.6V なので Vce は無視)

- 次に、ベース・バイアス部分のRb1とRb2を決めてみます。

バイアス(Rb2)に流す電流はベース電流の10倍以上は必要らしいので、2SC1815のhFEを180とした場合Ib=Ie÷180≒0.006mA 10倍からIb≒0.1mAにしてみます。

よってRb2=(Ve+0.6V)÷0.1mA≒26KΩ E系列では 27KΩになります。12VをRb1とRb2で分圧してるので、Rb1の電圧は、12V-2.6V=9.4V Rb1=9.4V÷0.1mA=94KΩになります。

- カップリング・コンデンサ、C1、C2はそれぞれ10μFにしました。

- 下図が各部品の値を決めたものです。

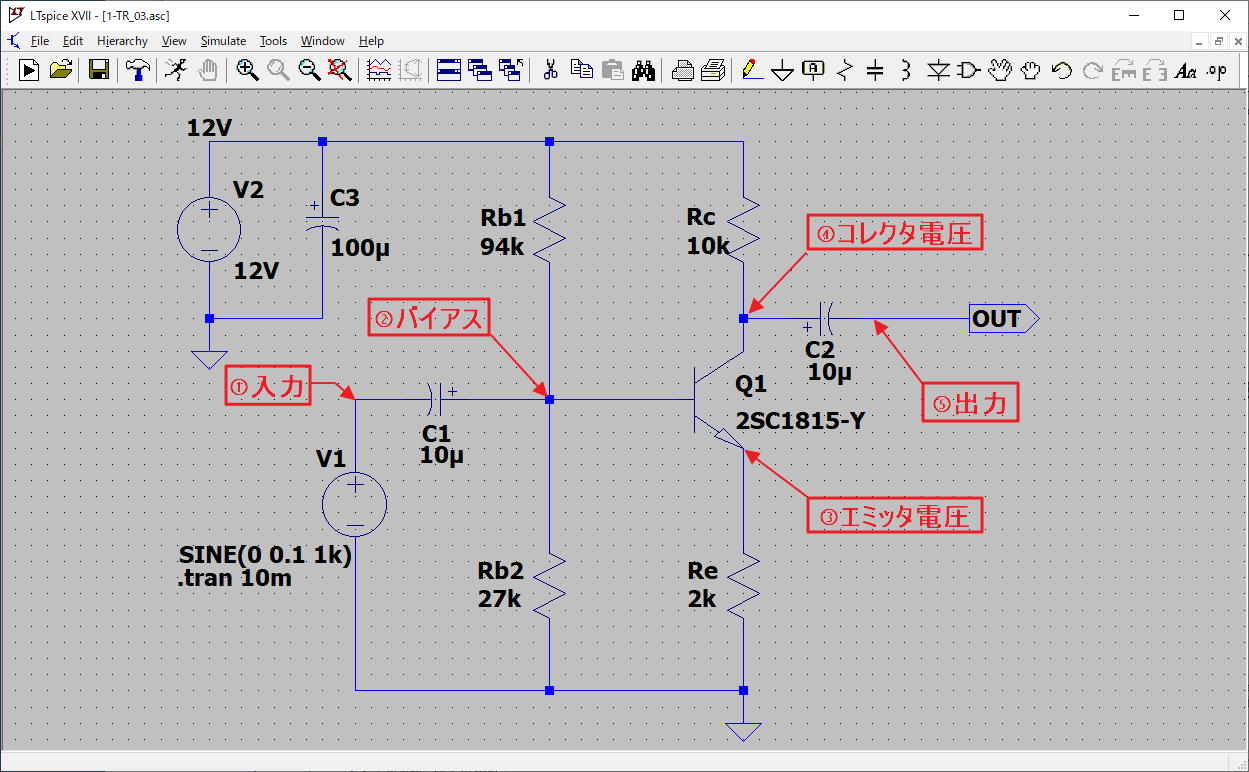

- 下図は測定ポイント、①入力、②バイアス、③エミッタ電圧、④コレクタ電圧、⑤出力を示したものです。

- この回路をシミュレーションします。

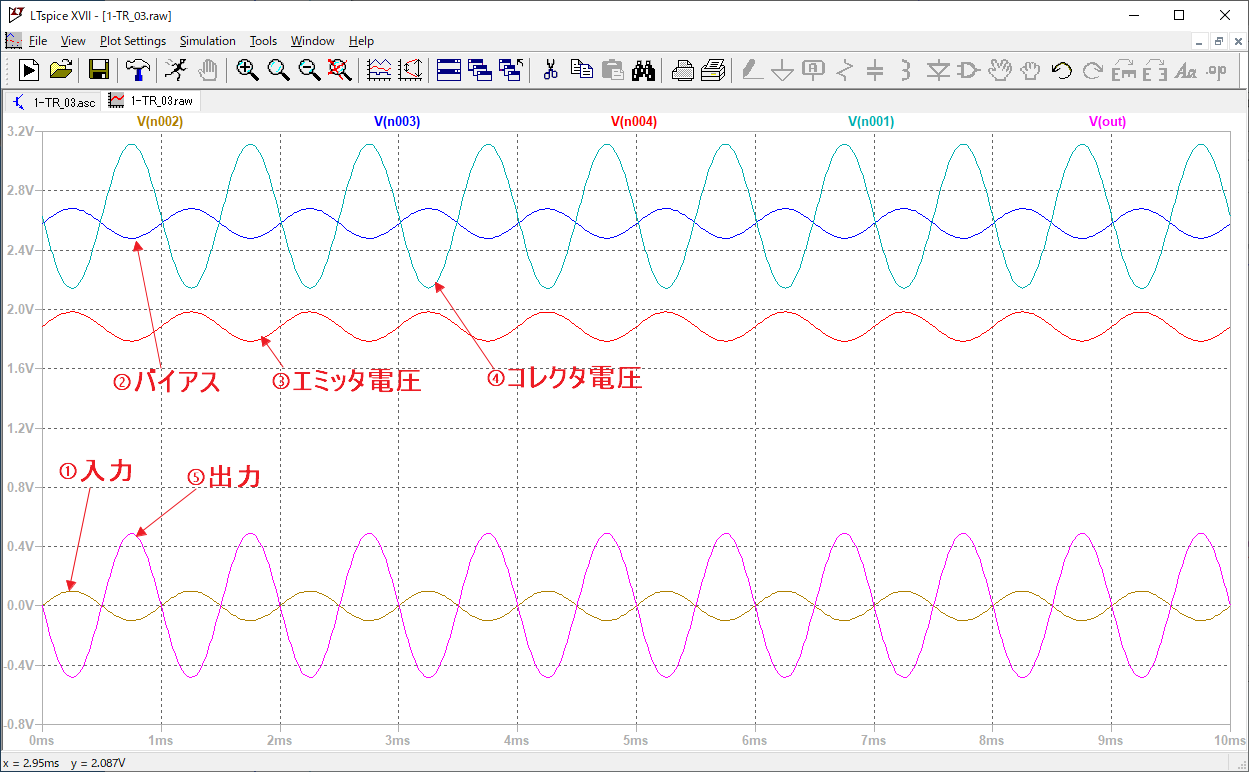

- シミュレーションの結果

バイアス電圧は:2.6V

Ve:1.88V

出力電圧:489.88mVで入力電圧100mVのほぼ5倍を示した。

シミュレーションの結果は計算結果とは多少ずれているが、ちゃんとバイアスが架かり増幅されているのが目で見て分かる。

|

|

- 終段 トランジスター回路

- 出力側の負荷の影響を受けにくいエミッタ・フォロウが良いそうです。エミッタ・フォロワはコレクタを接地してベースから入力した信号をエミッタから出力する仕組みだそうです。この時、エミッタの出力電位は常にベース(入力)よりも0.6V低い電位になります。つまり、電圧は増幅されずに、電流を増幅させるとのこと。

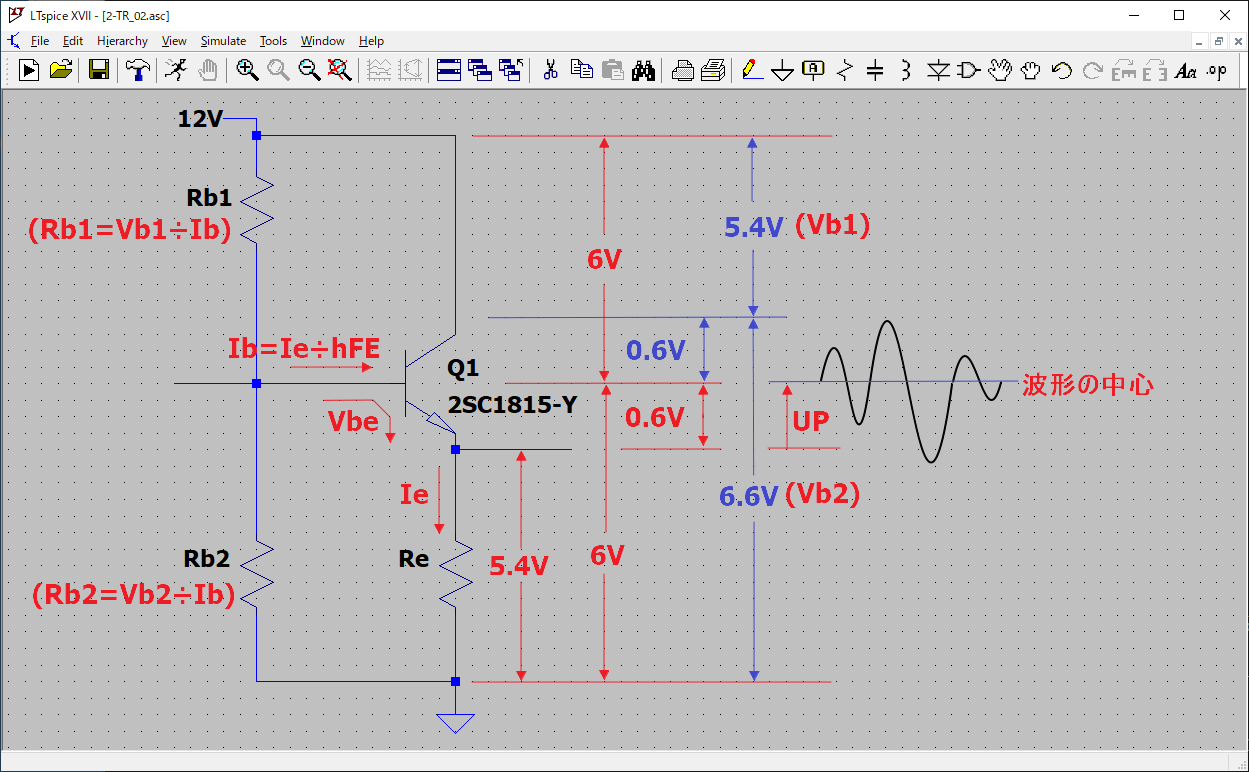

- 下図の定数を決めていきます。

- コンデンサーは初段と同じにして、バイアス抵抗 Rb1 Rb2とエミッタ抵抗 Re を決めます。

- バイアス抵抗 Rb1 Rb2

ポイントはエミッタから出力される電位を「出力波形が最大限に生かせるような中心」に合わせることだそうです。

Vbeの電圧降下0.6Vを考慮して出力波形の中心をあらかじめVbから0.6V高くしておいて、そこをバイアスの電位にすれば良いそうです。

つまり、電源電圧12Vの中心である6Vから0.6V高い位置ということで

6V + 0.6V = 6.6V (Vb2)

12V-6.6V=5.4V (Vb1)

もしくは 6V-0.6V=5.4V ということになります。

- 以上を考慮した結果が下図です。

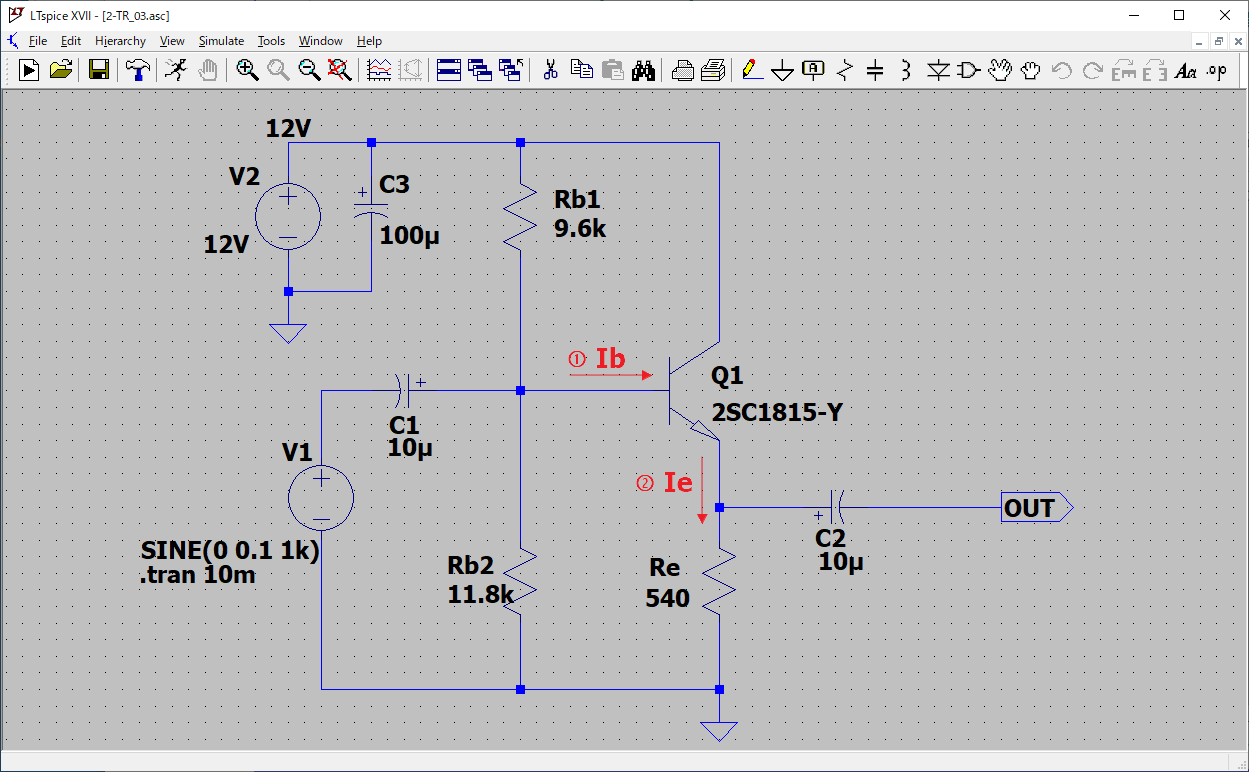

- Reを決めます、交流的にエミッタ抵抗が出力負荷抵抗と並列になり、合成抵抗になる為、エミッタ・フォロワの場合のIeは高めにしなければならないそうです。これは並列にした抵抗値が下がるためVeの電位も下がり、結果波形の下側がクリップしてしまうようです。

そこで、Ieを10mAとします。

以上は交流的に見ての事ですが、出力側カップリング・コンデンサの手前ということで直流的に見るので合成抵抗じゃなく、オームの法則から Re=(6V-0.6V)÷10mA=540Ω になります。

ベース電流は hFE=180 とすると 10mA÷180=0.056mA ベース・バイアス回路にはベース電流の10倍程度の電流が必要とのことで、0.056mA x 10=0.56mA 最低でも 0.56mA は必要のようです。

Rb2の電位は Vb2=6.6V から、Rb2=6.6V÷0.56mA≒11.8KΩ、Rb1=5.4V÷0.56mA=9.6KΩ

- 下図のように これで後段エミッタ・フォロワの定数が決まりました。

- この回路をシミュレーションします。

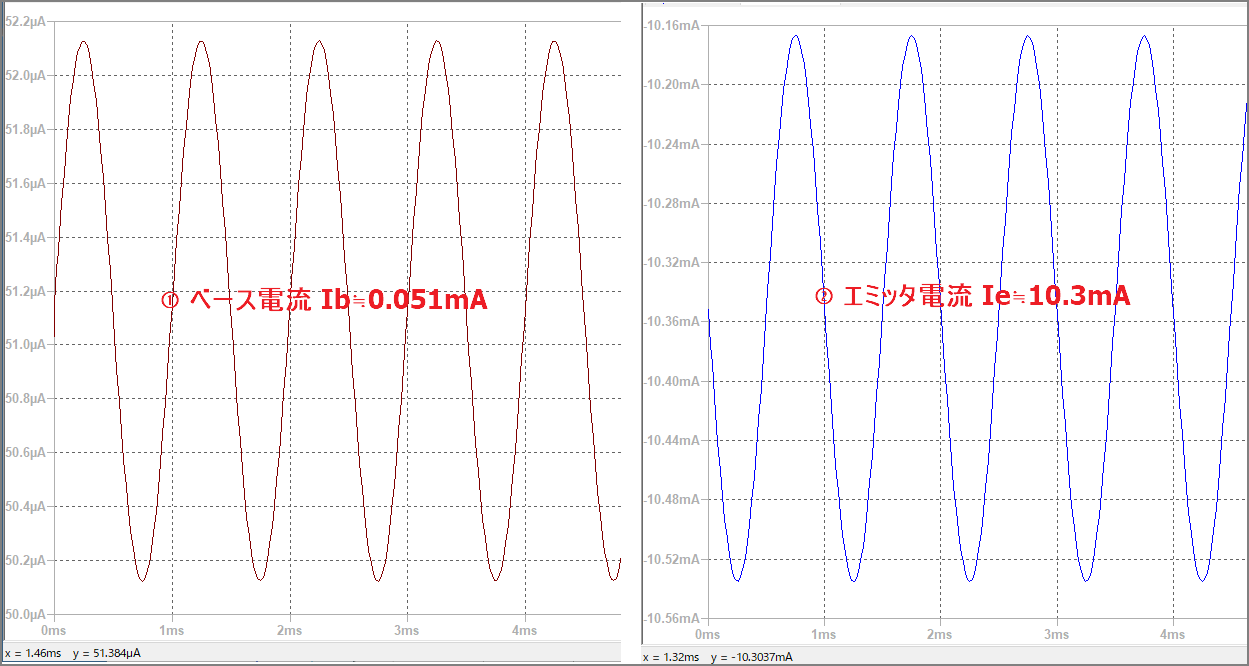

- シミュレーションの結果、Ib(0.051mA) x 180(hFE) ≒ Ie(9.18mA) と想定したエミッタ電流に近い値になったが、ベース電流の10倍の電流を元に RB2 を決めた時の 0.56mA を Ib が示すと思ったがその 1/10 の 0.051mA になったからくりが分からない。

|

|

- 初段回路と終段回路の結合

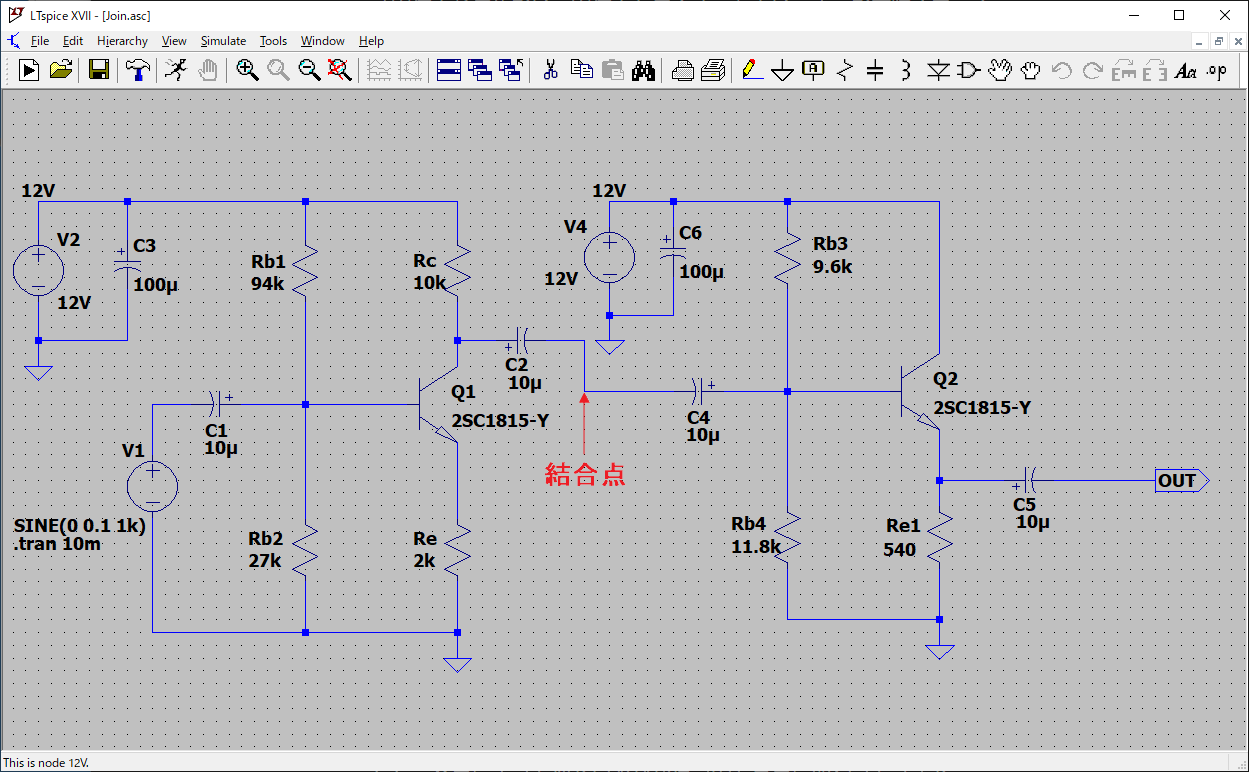

- そのまま結合すると、下図のようになる。

- 整理します、電源を1つに、バイパス・コンデンサ(C3 C6)を一つにします。

カップリング・コンデンサ C2 C4 を一つにします。

- 以下を試しましたがやはり理解が足りず旨く行きませんでした。

---( 厳密に終段のバイアスを計算せず、かつ最大限に増幅した際の波形を気にしないなら、初段の出力電位をそのまま後段のバイアス電位として使っても良いそうなのでその場合カップリング・コンデンサ C2(10μF) C4(10μF)、バイアス用抵抗 Rb3(9.6KΩ) Rb4(11.8KΩ)は省略出来るようです。)---

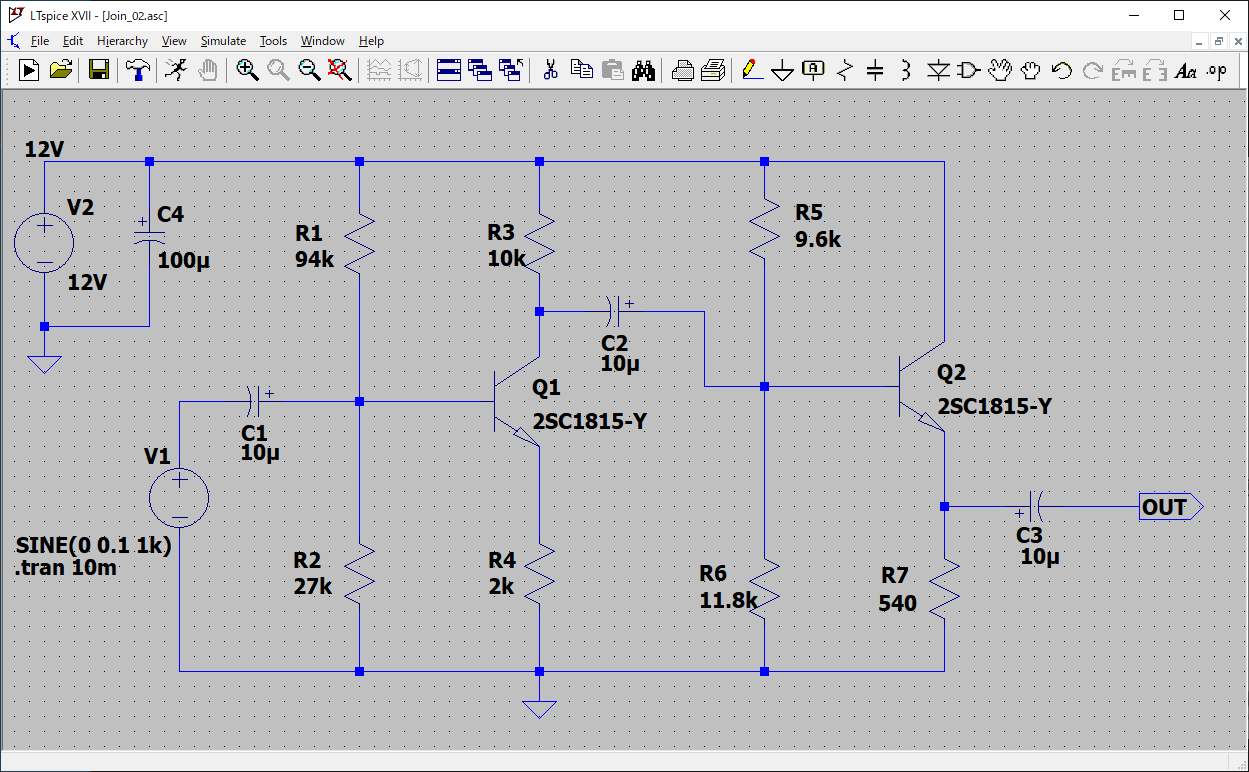

- 整理し結合した回路図です。

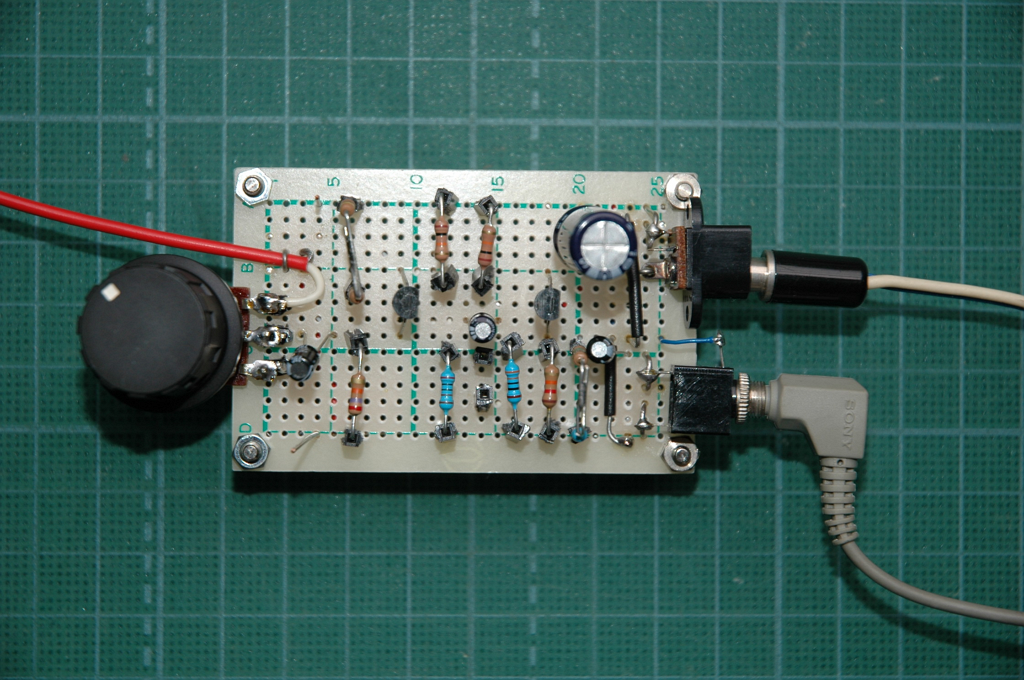

- この回路図を元にユニバーサル基板に部品を実装したものが下図です。

なお、C1 の前に入力調整用の 10KΩのボリュームを付けました、

- これで、一応音は出ました。全くの素人でも、簡単な回路図を書き、シミュレーションする事は、この LTspice で出来ましたが、それは「とは口」の事でありこれを使いこなすには、電気・電子を理解している方が、PC上で、信号源、電源、オシロスコープ、その他測定器類が無くてもある程度の目安に使うには便利なものと思います。

今回、はじめて 先ず信号源をどの様に設定したら良いか分からず、インターネット上で探しそれらしきものを真似して試す事の繰り返しでした、その点 LTspice は皆さんお使いの様子で沢山サンプルがあり助かりました。

また、バアスの理解が分からずベースへ流す電流とバイアス抵抗へ流す電流の意味が分かりませんし、今回の回路には入れませんでしたが、色々調べますと、初段の Q1 のエミッタへエミッタ・バイパス・コンデンサを入れてバイアスも崩さずに増幅度を上げるとの記事が多かったのですが、小生の回路で入れると信号が歪んだサイン波になってしまいました、これも理屈が分かっていればどの定数を変えれば良いかが分かるはずです。

今回は LTspice を知りこれ使って回路を試す切っ掛けが出来ました。回路の理解、LTspice でその回路をどの様な条件でシミュレーションするのか、浅学菲才の小生には荷が重すぎますが、幸いに時間は十分あります、遅々として進まないと思いますが面白そうです。

|